突破光罩尺寸限制、异质集成再进化:台积系统级芯片SoW是什么?

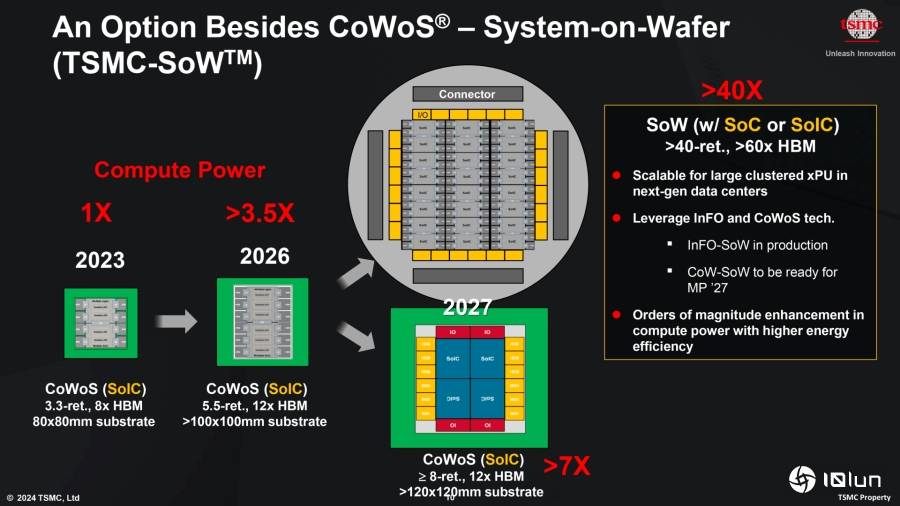

台积电业务开发资深副总裁张晓强(Kevin Zhang)于2024年北美技术论坛谈到多项最新技术,震撼业界。随着芯片微缩难度增加,台积电增加火力发展先进封装,提出“系统级芯片”(System on Wafer,SoW),在芯片上放置更多晶体管,使每瓦性能将达数量级提升,这对台积电先进封装生态又扮演什么关键角色?

台积电董事长刘德音曾说过“现在AI芯片短缺,缺的不是芯片,而是缺CoWoS封装产能”。为应对AI需求,台积电表示,客户越来越趋向采用CoWoS搭配系统集成芯片(SoIC)及其他组件的做法,以实现系统级封装(SiP)集成。

也因此,台积电针对系统级芯片技术提供新选项,让12英寸芯片能容纳大量晶粒,提供更多运算能力,大幅减少数据中心的使用空间,并将每瓦性能提升好几个数量级。

台积电SoW突破光罩尺寸极限,三年后运算能力提高40倍

过去数十年,芯片制造商主要通过缩小晶体管所占面积和互联规模,提高处理器上逻辑芯片密度,但这方法已逐渐不管用,因此企业逐渐转向先进封装,使用更多的硅来制造处理器。

然而,单一芯片的尺寸受限于曝光设备的处理极限,或者说是光罩尺寸极限(reticle limit),该极限目前为800平方毫米,所以若要在GPU中使用更多硅,就需要用两个以上裸晶(Die)制作,而关键在于将这些裸晶连接,使信号以极少能耗,从一个芯片快速传递至另一个芯片,宛如大芯片一样。

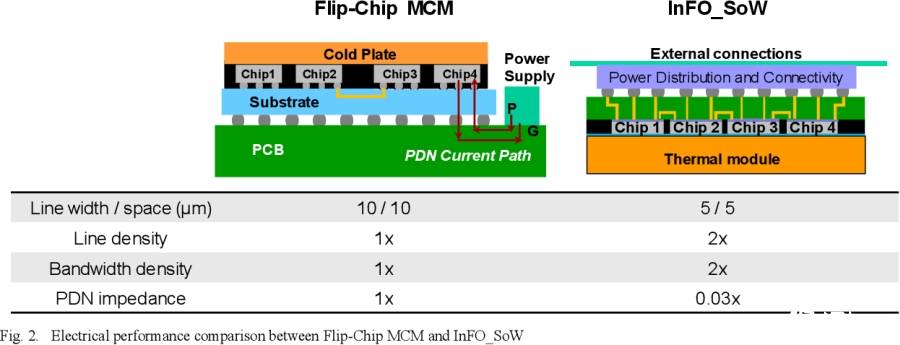

台积电SoW能解决光罩尺寸极限和良率问题。从已测试逻辑裸晶开始,先尽可能减少缺陷。这些裸晶放在载体芯片上,裸晶间空白点填补;接着再用InFO技术构建一层高密度互联层,连接逻辑芯片,目的是提高芯片间数据带宽(bandwidth),使其如大型芯片运行。

InFO-SoW剖面图。(Source:semanticscholar)

目前首款SoW产品采用以逻辑芯片为主的集成型扇出(InFO)技术,另一个CoWoSSoW芯片堆栈版本预计2027年量产,但目前不确定采用CoWoS-R/L/S哪种技术。据悉CoWoSSoW预先测试的逻辑芯片、HBM内存会通过高密度互联和硅穿孔(TSV)垂直贯穿,连接到硅基板。

从台积电投影看来,可能分为两种技术新选择,2026年即将推出的是CoWoS(SOIC)先进封装(即图左二),计划采用光罩尺寸达5.5倍,可采用12个HBM内存堆栈,以及容纳更大基板,其基板尺寸达100×100mm。

至于SoW技术(图中上圆形处)是将系统及芯片集成放在硅芯片上,图中的方形灰块是SoIC芯片连接HBM内存;黄色处是I/O,即信号的输入与输出;绿色处即为经过封装的状态。

业界人士透露,目前台积电InFO技术和CoWoS技术已并列为2.5D技术,以前定义是InFO密度较低、价格较便宜,但现在依据芯片与重布线层(RDL)的先后顺序,可分为先芯片(Chip First)及后芯片(Chip Last)等两类制程。其中,CoWoS-R利用集成InFO技术,中介层使用RDL布线来连接小芯片之间,适合HBM和SoC集成。

也因此,业界人士表示InFOSoW和CoWoSSoW都是系统级芯片封装,台积电重点在“系统级”,即可放入更多HBM内存跟更多裸晶,而台积电有能力将这些芯片封装在一起,形成一个系统,未来适合AI和自动驾驶应用;另一位业界人士透露,SoW整片芯片就是一个封装(package)。

Flip-Chip MCM与InFO_SoW性能比较及剖面图。(Source:semanticscholar)

台积电首款InFO_SoW产品,即是特斯拉超级计算机自制芯片Dojo,将提供高速运算定制化需求,且不需要额外PCB载板,就能将相关芯片集成散热模块,加速生产流程。

另据业界说法,SoW技术本身能实现异质集成,将不同制程、不同成本芯片进行集成,例如采用特殊制程DRAM或模拟芯片,通过SoW技术将与逻辑芯片进行封装。

(首图来源:shutterstock)