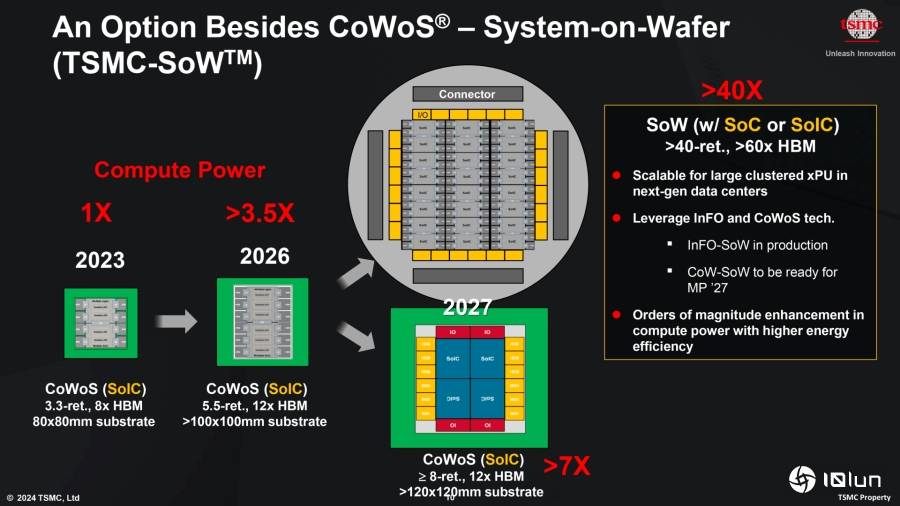

台積電業務開發資深副總裁張曉強(Kevin Zhang)於2024年北美技術論壇談到多項最新技術,震撼業界。隨著晶片微縮難度增加,台積電增加火力發展先進封裝,提出「系統級晶片」(System on Wafer,SoW),在晶片上放置更多電晶體,使每瓦性能將達數量級提升,這對台積電先進封裝生態又扮演什麼關鍵角色?

台積電董事長劉德音曾說過「現在AI晶片短缺,缺的不是晶片,而是缺CoWoS封裝產能」。為應對AI需求,台積電錶示,客戶越來越趨向採用CoWoS搭配系統集成晶片(SoIC)及其他組件的做法,以實現系統級封裝(SiP)集成。

也因此,台積電針對系統級晶片技術提供新選項,讓12英寸晶片能容納大量晶粒,提供更多運算能力,大幅減少數據中心的使用空間,並將每瓦性能提升好幾個數量級。

台積電SoW突破光罩尺寸極限,三年後運算能力提高40倍

過去數十年,晶片製造商主要通過縮小電晶體所占面積和互聯規模,提高處理器上邏輯晶片密度,但這方法已逐漸不管用,因此企業逐漸轉向先進封裝,使用更多的矽來製造處理器。

然而,單一晶片的尺寸受限於曝光設備的處理極限,或者說是光罩尺寸極限(reticle limit),該極限目前為800平方毫米,所以若要在GPU中使用更多矽,就需要用兩個以上裸晶(Die)製作,而關鍵在於將這些裸晶連接,使信號以極少能耗,從一個晶片快速傳遞至另一個晶片,宛如大晶片一樣。

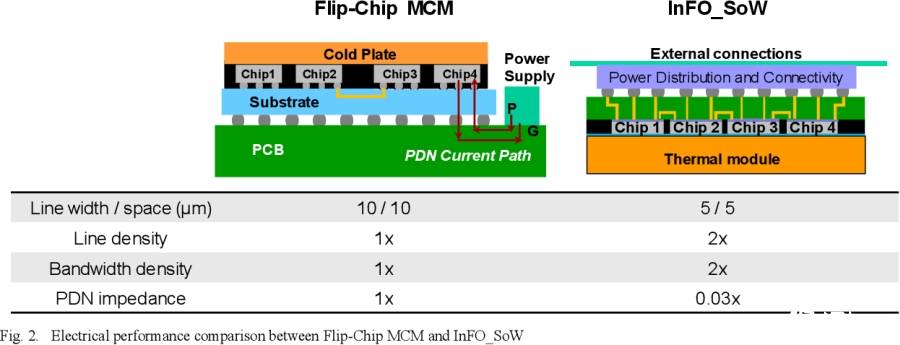

台積電SoW能解決光罩尺寸極限和良率問題。從已測試邏輯裸晶開始,先儘可能減少缺陷。這些裸晶放在載體晶片上,裸晶間空白點填補;接著再用InFO技術構建一層高密度互聯層,連接邏輯晶片,目的是提高晶片間數據帶寬(bandwidth),使其如大型晶片運行。

InFO-SoW剖面圖。(Source:semanticscholar)

目前首款SoW產品採用以邏輯晶片為主的集成型扇出(InFO)技術,另一個CoWoSSoW晶片堆棧版本預計2027年量產,但目前不確定採用CoWoS-R/L/S哪種技術。據悉CoWoSSoW預先測試的邏輯晶片、HBM內存會通過高密度互聯和矽穿孔(TSV)垂直貫穿,連接到矽基板。

從台積電投影看來,可能分為兩種技術新選擇,2026年即將推出的是CoWoS(SOIC)先進封裝(即圖左二),計劃採用光罩尺寸達5.5倍,可採用12個HBM內存堆棧,以及容納更大基板,其基板尺寸達100×100mm。

至於SoW技術(圖中上圓形處)是將系統及晶片集成放在矽晶片上,圖中的方形灰塊是SoIC晶片連接HBM內存;黃色處是I/O,即信號的輸入與輸出;綠色處即為經過封裝的狀態。

業界人士透露,目前台積電InFO技術和CoWoS技術已並列為2.5D技術,以前定義是InFO密度較低、價格較便宜,但現在依據晶片與重布線層(RDL)的先後順序,可分為先晶片(Chip First)及後晶片(Chip Last)等兩類製程。其中,CoWoS-R利用集成InFO技術,中介層使用RDL布線來連接小晶片之間,適合HBM和SoC集成。

也因此,業界人士表示InFOSoW和CoWoSSoW都是系統級晶片封裝,台積電重點在「系統級」,即可放入更多HBM內存跟更多裸晶,而台積電有能力將這些晶片封裝在一起,形成一個系統,未來適合AI和自動駕駛應用;另一位業界人士透露,SoW整片晶片就是一個封裝(package)。

Flip-Chip MCM與InFO_SoW性能比較及剖面圖。(Source:semanticscholar)

台積電首款InFO_SoW產品,即是特斯拉超級計算機自製晶片Dojo,將提供高速運算定製化需求,且不需要額外PCB載板,就能將相關晶片集成散熱模塊,加速生產流程。

另據業界說法,SoW技術本身能實現異質集成,將不同製程、不同成本晶片進行集成,例如採用特殊製程DRAM或模擬晶片,通過SoW技術將與邏輯晶片進行封裝。

(首圖來源:shutterstock)