文:王世權 編輯:練怡萍

2024年4月12日,由華強電子網主辦的「2024半導體產業發展趨勢大會暨2023年度(第十六屆)華強電子網優質供應商&電子元器件行業優秀國產品牌頒獎盛典」在深圳南山華僑城洲際大酒店圓滿舉辦!馮明憲博士受邀參加芯榜承辦的分論壇之「晶片與智能硬體融合創新論壇」,並做「AI時代HBM產業發展探討」主題報告。

在報告中,馮明憲博士提出:HBM是AI半導體性能進一步提升並突破算力瓶頸的關鍵,隨著AI技術加速創新應用,HBM市場規模也將急劇增長,2026年有望達到230億美元,進而帶動存儲市場進入新一輪的上漲周期。報告對HBM技術、產業發展進行了系統分析,並對以HBM為代表的存儲產業為基礎的兩岸AI半導體合作及投資機遇進行了展望。

下面就馮明憲博士的報告內容與大家分享:

二、HBM技術、工藝、市場分析

高帶寬存儲器,簡稱HBM,即High Bandwidth Memory,採用了3D堆疊技術,將多個DRAM晶片堆疊在一起,從而實現了更高容量,更大的存儲帶寬和更低的延遲,被廣泛應用於高性能計算、數據中心等領域。

目前HBM大都採用了標準化設計:HBM存儲器堆棧通過微凸塊連接到HBM堆棧中的矽通孔(TSV或連接孔),並與放置在基礎封裝層上的中間件相連,中間件上還安裝有處理器,提供HBM到處理器的連接。與此同時,HBM通過控制晶片對多個DRAM晶片進行控制,使它們能夠同時讀取或寫入數據,從而提高了存儲帶寬和數據處理能力。這樣的設計與普通的DRAM相比,能夠同時垂直連接多個DRAM並顯著提升數據處理速度,這也是HBM具備更高存儲帶寬和更低延遲的關鍵所在。

自2013年第一代HBM誕生以來,隨著技術的不斷發展,HBM也經歷了HBM2(第二代)、HBM2E(第三代)、HBM3(第四代)、HBM3E(第五代)的順序疊代,最新的HBM3E是HBM3的擴展版本,速率達到了8Gbps。

1、HBM關鍵技術

在HBM設計製造過程中,先進封裝是最關鍵技術,包括TSV(矽通孔)、Bumping(凸點製造)、堆疊鍵合等技術,另外在與邏輯晶片共封時又另外使用中介層、CoWoS等技術。

HBM結構及相關技術圖示

(1)TSV工藝

TSV矽通孔是實現容量和帶寬擴展的核心,根據國際半導體技術發展路線圖(ITRS),TSV定義為:連接矽圓片兩面並與矽襯底和其他通孔絕緣的電互連結構。由此可見,TSV是一種垂直互連結構,特點是穿透矽襯底,並實現從對應電路層一面到另一面的電氣連接。根據矽通孔的定義,可以知道,TSV的基本結構包括穿透矽襯底的導電通道,以及與襯底之間的絕緣隔離層。並且,為了實現襯底上下面的電氣連接,還需要正面和背面的互連層,以實現信號的互連和再分布。

TSV概念最早可以追溯到1958年,威廉·肖克利(WilliamShockley)提出了一份專利申請「Semiconductive wafer and method of making the same」首次提出了矽通孔(TSV)結構,並獲得專利批准。肖克利提出的TSV主要作用有兩個,其一,實現晶片正反之間的電導通,其二,是有利於熱管理,即更好的釋放熱量並提高熱管理性能。經過幾十年的發展,目前應用最廣泛的是Cu-TSV,即矽通孔(TSV)中填充銅,而使用銅作為TSV填充材料的3D集成封裝,主要是日本超級先鋒協會首創電子技術聯盟(1999-2003年)率先實現的。

2006年,三星電子發布了較為簡單的存儲晶片堆疊示意圖,這些晶片大部分屬於DRAM(動態隨機存取存儲器)或者I/O數量少於100的NAND快閃記憶體(I/O數量比較確切的是78個)。這種存儲晶片附在有機基板上,即使採用8個晶片堆疊,它們總體的厚度(560μm)仍然小於普通晶片的厚度,但是考慮到綜合生產成本與引線鍵合技術的成熟封裝量產的競爭,使用矽通孔(TSV)技術的存儲器晶片堆疊並未進行大規模量產。

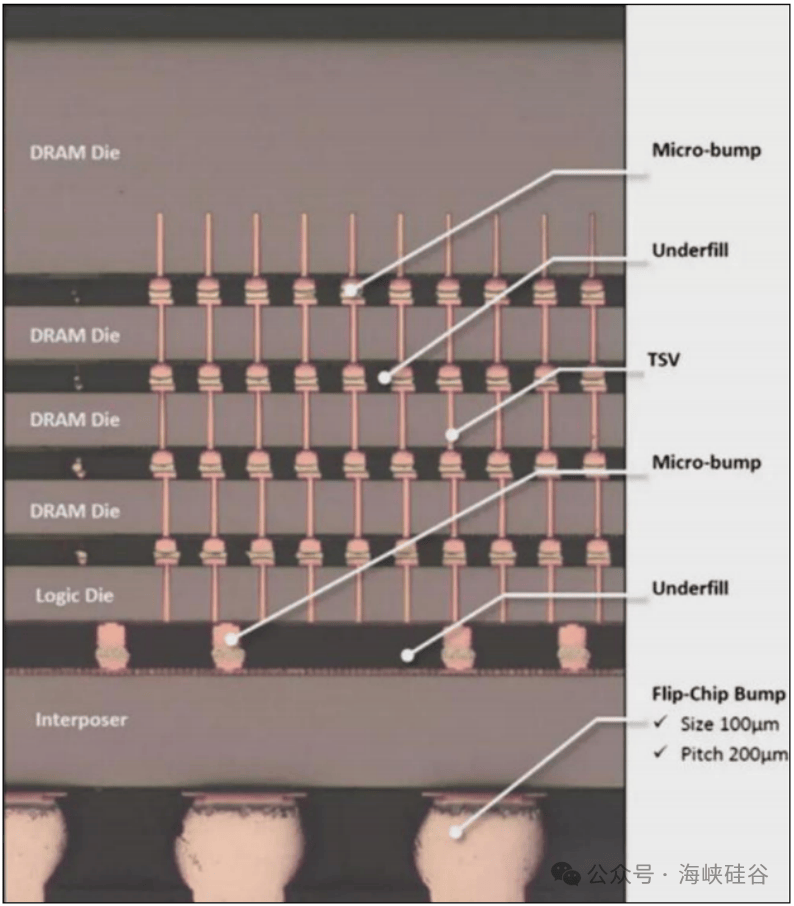

在HBM設計製造中,通過在整個矽晶圓厚度上打孔,在晶片正面和背面之間形成數千個垂直互連。在HBM中多層DRAMdie堆疊,通過矽通孔和焊接凸點連接,且只有最底部的die能向外連接到存儲控制器,其餘管芯則通過內部TSV實現互連。

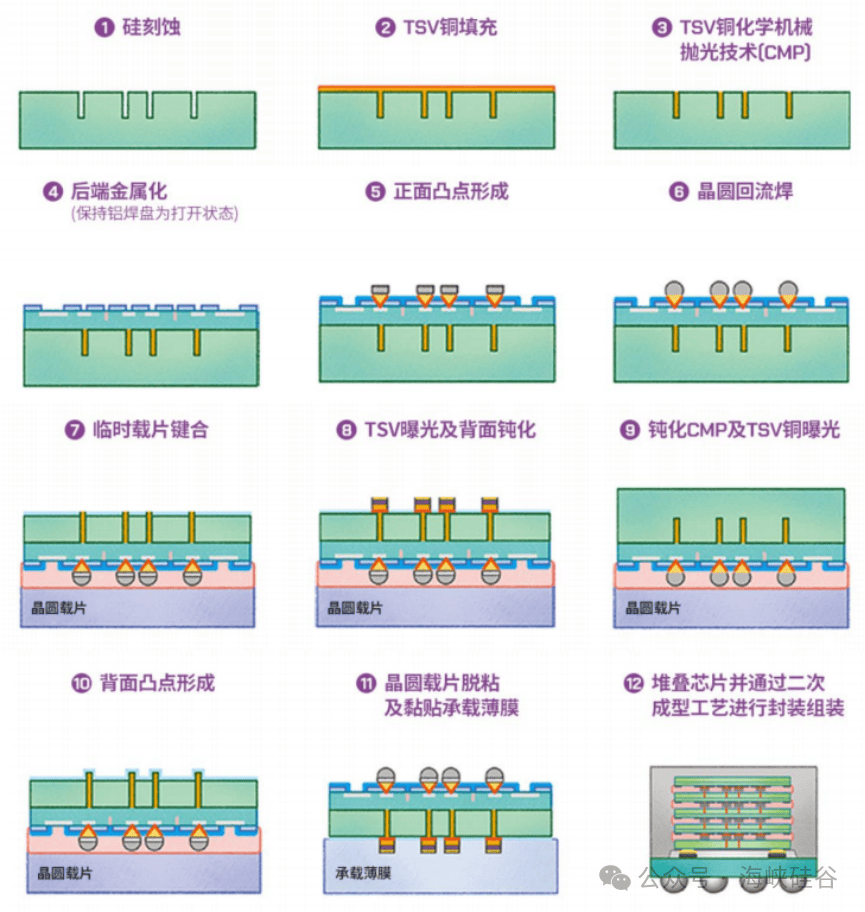

TSV工藝包含晶圓的表面清洗、光刻膠圖案化、干法/濕法蝕刻溝槽、氣相沉積、通孔填充、化學機械拋光等幾種關鍵工藝,運用到晶圓減薄機、掩膜設備、塗膠機、雷射打孔機、電鍍設備、濺射台、光刻機、刻蝕機,同時配套的電鍍液、靶材、特種氣體、塑封料等。

TSV工藝流程

HBM中的TSV結構

(2)微凸塊技術

凸塊製造技術(Bumping)是一項關鍵的先進封裝技術,它通過在晶片表面製造金屬凸塊來提供電氣互連的「點」接口。這一技術在多個先進封裝應用領域廣泛應用,包括FC、WLP、CSP、以及3D封裝等。

凸塊指的是定向生長在晶片表面的金屬凸起結構,它們與晶片焊盤直接或間接相連,具備金屬導電特性。凸塊工藝位於整個產業鏈的關鍵位置,處於集成電路製造和封裝測試之間,因此被視為先進封裝領域的核心技術之一。

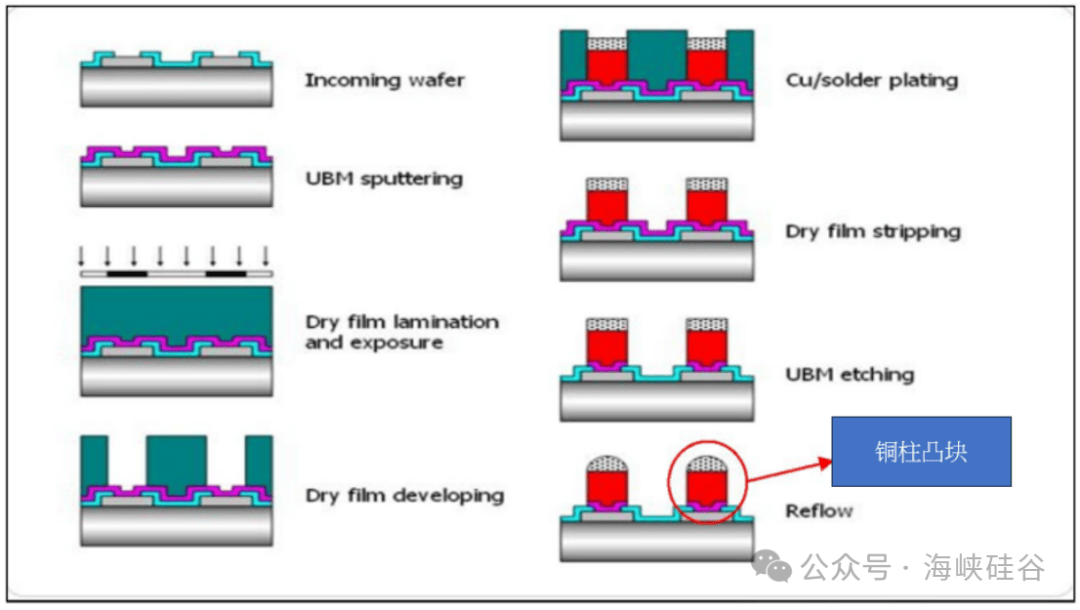

其技術的基本原理如下:

晶圓製程後的加工:Bumping技術通常在晶圓製程的後階段進行。晶圓製程包括完成IC電路部分的加工,而Bumping則在此之後進行,用以在晶圓的I/O埠的Pad上形成焊料凸點。

凸點形成過程:在Bumping過程中,通常會將焊料材料(通常是錫合金)塗覆或以其他方式添加到晶圓的特定區域,這些區域通常是I/O埠的Pad。隨後,焊料會被加熱,以形成小型的凸點,這些凸點用於連接晶片和其他封裝組件,如基板(substrate)。

用途:Bumping技術的主要目標是確保晶片與其他封裝組件之間的可靠連接。這種連接可以通過焊接等方法來實現,以便有效傳輸信號和能量。

隨著封裝技術的演進,凸塊技術也向著更高密度、更小微間距方向發展。因此,在2.5D與3D先進封裝中,凸塊的尺寸至關重要,一般銅微凸塊比焊球/凸塊更小,可在封裝中實現更多I/O。當前,先進封裝技術的微凸塊間距最小達40μm,這相當於20μm至25μm的凸塊尺寸,裸晶上相鄰凸塊之間的間距為15μm。

對於小於400μm的間距,在封裝上有另外一些選擇,即首先可以使用現有的凸塊技術研發新的封裝技術,以突破技術瓶頸,將當前400μm間距向下微縮至100μm。或者,另一種選擇是被稱為銅混合鍵合的新技術。在混合鍵合技術中,裸晶的連接並非通過封裝中的凸塊。相反,該技術利用微小的銅對銅互連,實現比傳統封裝具有更多I/O的更窄間距封裝。對於封裝技術來說,混合鍵合的間距至少在10μm及以下。

在第一種方案中,隨著焊料/銅凸點技術逐漸向更窄間距微縮,對於新材料、新工藝和新工具的需求越來越多,隨之挑戰也大幅增加。而第二種方案,則面臨著成本高昂技術苦難的局面,僅能應用在高端產品上,有較大的技術研發與應用局限。

銅柱凸塊製程示意圖

(3)鍵合工藝

在HBM產品開發之初,HBM主要採用「TSV+Bumping」+TCB鍵合方式堆疊(TSV一般由晶圓廠完成,封測廠可在堆疊環節進行配套)。

其中,熱壓鍵合TCB是由貝爾實驗室的三位科學家O. L. Anderson、H. Christensen和P. Andreatch在1955-58年期間開發完成的。相關資料介紹,熱壓鍵合主要用於創建原子級金屬鍵合。它利用力和熱量來促進原子在晶格之間遷移,從而形成清潔、高導電性和堅固的鍵合。通常,TCB被用於垂直集成器件的CMOS工藝、金引線和表面之間固態鍵合的順應鍵合(compliant bonding)、用於將晶片凸塊鍵合到基板的倒裝晶片應用以及用於連接微型組件的熱壓鍵合。

但隨著堆疊層數的增加散熱效率很差,TCB不再滿足需求,海力士率先引入MR-MUF回歸大規模回流焊工藝,即晶片之間用液態環氧模塑料作為填充材料,導熱率比TC-NCF中的非導電薄膜高很多。

MR-MUF工藝流程

MR-MUF(Mass Reflow Molded Underfill )是將半導體晶片堆疊後,為了保護晶片和晶片之間的電路,在其空間中注入液體形態的保護材料,並固化的封裝工藝技術。與每堆疊一個晶片鋪上薄膜型材料的方式對比 工藝效率高,散熱方面也更有效。

其具體步驟如下:

1)連接晶片的微凸塊採用金屬塑封材料;

2)一次性融化所有的微凸塊,連接晶片與電路;

3)晶片與晶片之間或者晶片與載板之間的間隙填充,絕緣和塑封同時完成。

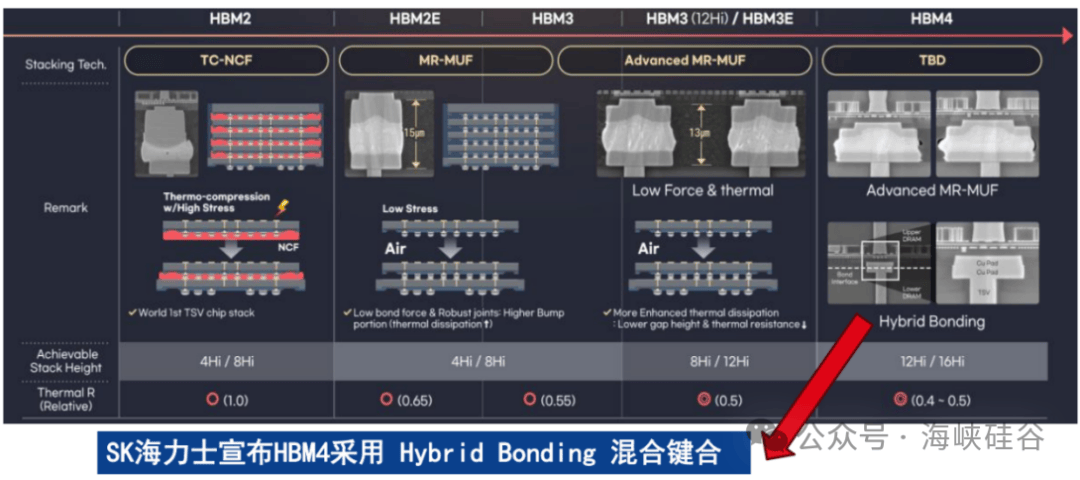

MR-MUF不僅能提高生產力,還能帶來更高性能的HBM。在晶片之間,環氧模塑料用作間隙填充材料,其導熱率比TC-NCF中的非導電薄膜高得多。在SK海力士和三星電子、美光的HBM市場競爭中,SK海力士領先三星電子和美光的關鍵就在於MR-MUF工藝。三星電子從HBM生產之初就一直採用熱壓縮非導電薄膜(TC-NCF)工藝,而SK海力士採用的則是批量回流模製底部填充(MR-MUF)工藝。技術路線圖顯示,從HBM2e開始,海力士放棄了TC-NCF工藝,改用MR-MUF工藝,實現了更低的鍵合應力和更優的散熱性能。海力士HBM3e將採用改進的MR-MUF工藝,降低鍵合應力,提升散熱性能,增加堆疊層數。HBM4有可能採用混合鍵合(Hybrid bonding)工藝,進一步降低TSV DRAM層與層之間的間隙,實現更高層數堆疊。

海力士MR-MUF工藝和三星TC-NCF工藝比較

然而,TCB技術仍有著一定的優勢,即是因為這項技術解決了標準倒裝晶片(standard flip chip)的幾個主要問題:例如熱量從晶片頂部施加,因此只有晶片和C4焊料連接會升溫,可以最大限度地減少任何基板翹曲問題;同時,這種鍵合方式確保均勻粘合,沒有間隙變化或傾斜;最後,這種粘合幾乎沒有空隙,也沒有污染。

因此,目前HBM市場暫時處於TCB與MR-MUF共存的時期。然而,無論是TCB技術還是MR-MUF工藝均存在著一定的局限性,難以實現更小的間距,混合鍵合Hybrid Bonding方案由此登上了舞台。

混合鍵合,是指在一個鍵合步驟中同時鍵合電介質(dielectric)和金屬鍵合焊盤(metal bond pads)。具體而言,混合鍵合有兩種類型:一種是晶圓到晶圓(wafer-to-wafer:W2W)鍵合,這種方式更加成熟,但限制了相同晶片尺寸的組合;另一種是晶片到晶圓(die-to-wafer:D2W)鍵合,它涉及更多的工藝步驟以及將晶片單獨放置在載體晶圓或玻璃上(集體晶片到晶圓方法)。

在這兩種情況下,通過BEOL金屬化處理的兩片晶圓都會經歷鍵合電介質的CVD、阻擋層的鑲嵌沉積,然後銅填充、電介質的平坦化(帶有輕微的銅凹進)、等離子體激活以準備鍵合、對準、室溫鍵合,並退火以形成銅焊盤的電連接。然後將矽晶圓背面研磨至最終厚度(通常<100nm),之後切割,然後進行最終組裝和封裝。

與微凸塊(microbumps)相比,過渡到混合鍵合的原因相當簡單。那就是3D內存堆棧和異構集成(超越摩爾時代的兩個參與者)需要極高的互連密度,如上所述,混合鍵合可以滿足這一需求;與本身支持高密度互連方案的微凸塊相比,混合鍵合可提供更小尺寸的I/O端子和減小間距的互連。每個晶片之間的間隔距離取決於微凸塊的高度,但在混合鍵合中該距離幾乎為零。

因此,混合鍵合互連方案可以顯著降低整體封裝厚度,在多晶片堆疊封裝中甚至可能高達數百微米。為此,自十多年前在CMOS圖像傳感器中首次亮相,混合鍵合逐漸走向了3D NAND,甚至連DRAM和HBM,也對混合鍵合產生了興趣。今年二月更是有消息傳出,英特爾下一代Xeon「Clearwater Forest」CPU採用一個名為「Foveros Direct」的混合鍵合的3D堆疊技術。

而在去年12月舉辦的IEDM 2023上,SK海力士宣布,其已確保HBM製造中使用的混合鍵合工藝的可靠性。消息表示,HBM晶片的標準厚度為720 µm。預計將於2026年左右量產的第6代HBM(HBM4)需要垂直堆疊16個DRAM,這對當前的封裝技術滿足客戶滿意度來說是一個挑戰。因此,Hybrid Bonding工藝在下一代HBM中的應用被業界認為是必然的。

SK海力士堆疊鍵合技術路線圖

而據了解,包括台積電、英特爾、三星、SK海力士、美光、索尼、豪威科技、鎧俠、西部數據、Besi、芝浦電子、東京電子、應用材料、EV Group、SUSS Microtec、SET和博世等廠商都對混合鍵合產生了興趣,眾多產業鏈大廠的加入,勢必將加速混合鍵合的研發應用速度。

(4)CoWoS技術

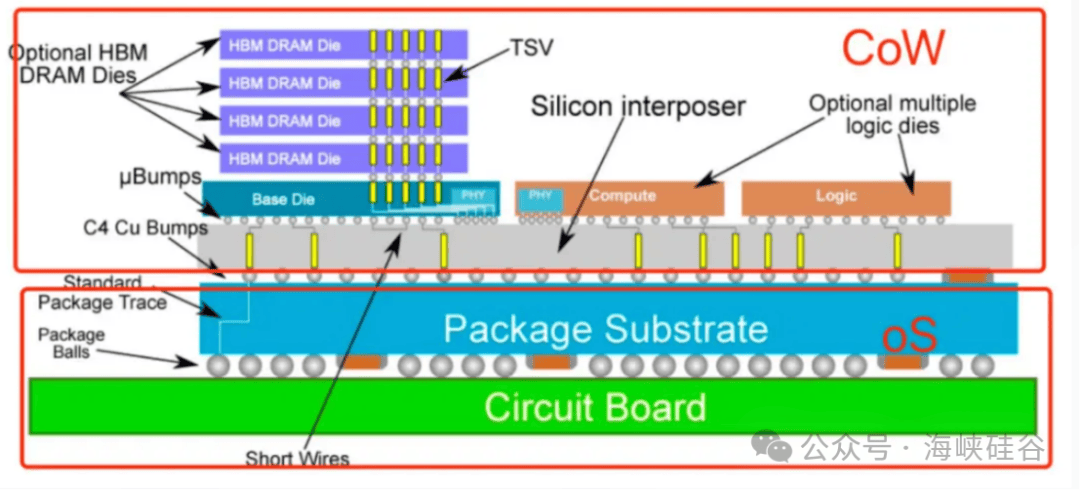

CoWoS(Chip On Wafer On Substrate)是一種2.5D的整合生產技術,由CoW和oS組合而來:先將晶片通過Chip on Wafer(CoW)的封裝製程連接至矽晶圓,再把CoW晶片與基板(Substrate)連接,整合成CoWoS。

Cowos技術的結構

CoWoS技術的核心概念是將多顆不同的晶片堆疊在同一塊矽中介層上,以實現它們之間的互聯。在這個矽中介層中,台積電採用微凸塊(μBumps)和矽穿孔(TSV)等先進技術,代替了傳統的引線鍵合方式,用於連接不同晶片,這顯著提高了互聯密度和數據傳輸帶寬。通過CoWoS技術,台積電實現了提升系統性能、降低功耗和縮小封裝尺寸的目標,使其在封裝技術領域保持領先地位,為超越摩爾定律奠定了堅實的基礎。

CoWoS是台積電的一種2.5D封裝技術,其中多個有源矽晶片(通常包括邏輯晶片和HBM堆棧)被整合到無源矽中介層上。這個中介層充當了頂部有源晶片之間的通信層,然後將中介層和有源矽連接到包含I/O接口的封裝基板上,最終用於系統的PCB上。

HBM和CoWoS技術是相互補充的。由於HBM需要高密度焊盤和短距離連接,這種要求只能通過2.5D封裝技術,例如CoWoS來實現,而無法在常規的PCB或封裝基板上實現。CoWoS以相對合理的成本提供了最高的互連密度和最大的封裝尺寸。目前,幾乎所有的HBM系統都採用CoWoS封裝,而幾乎所有領先的數據中心GPU都是台積電採用CoWoS技術封裝的。這使得台積電在這一領域保持了領先地位。

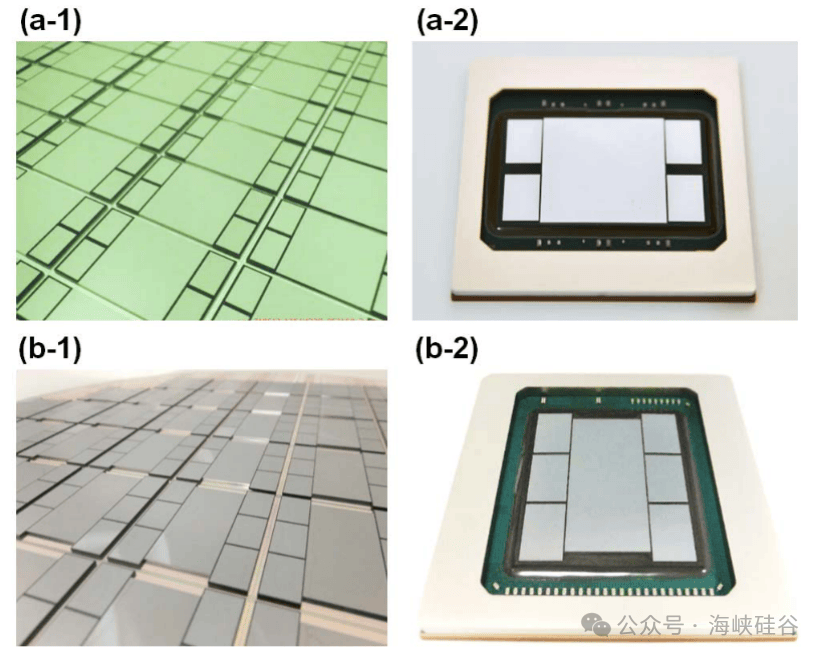

以HBM2為例,下圖顯示了兩種不同平面圖布置的CoW後和基板上(oS)後的實樣。

CoW晶圓和CoWoS封裝視圖顯示了兩種類型的中介層平面圖。(a-1)和(a-2)一個SoC和四個HBM2,即「1 + 4」。(b-1)和(b-2)一個SoC和六個HBM2,或「1 + 6」

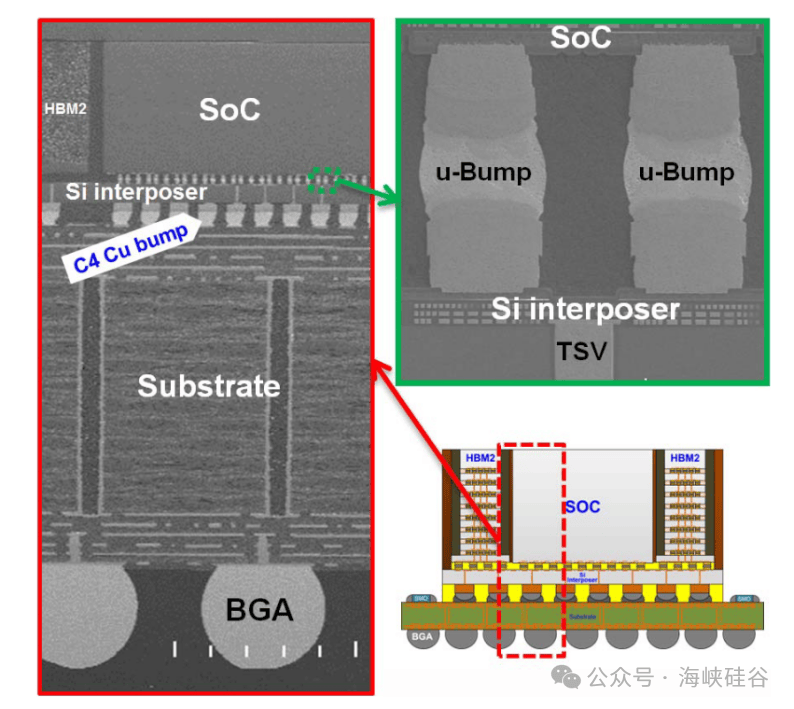

下圖則顯示了封裝橫截面圖像的全局視圖,其中包含HBM2、片上系統(SoC)、中介層和基板的所有組件。

封裝的光學橫截面圖像顯示了所有組件和良好控制的封裝共面性

下圖顯示了CoWoS-2中矽中介層上uBump、TSV、C4 Cu凸塊的主要特徵。

SEM橫截面圖像顯示uBump、矽中介層、TSV、C4 Cu凸塊、基板、球柵陣列和先進節點SoC以及CoWoS-2封裝中的HBM2

2、HBM歷代產品及技術發展路線

目前,HBM已經演變到了第五代,在SK海力士、三星、美光三大DRAM大廠推動下,性能表現持續提升,HBM的層數、容量、帶寬指標不斷升級,目前最先進的HBM3e版本,理論上可實現16層堆疊、64GB容量和1.2TB/s的帶寬,分別為初代HBM的2倍、9.6倍和4倍。

疊代HBM晶片參數對比

對比HBM的五代產品,從HBM1到HBM3e都保留了相同的1024位(每個堆棧)接口,即具有以相對適中的時鐘速度運行的超寬接口,為了提高內存傳輸速率,預計下一代HBM4可能需要對高帶寬內存技術進行更實質性的改變,即從更寬的2048位內存接口開始。

相關報道顯示,HBM4在DRAM堆疊方面,2048位內存接口需要大幅增加內存堆疊的矽通孔數量。同時,外部晶片接口需要將凸塊間距縮小到遠小於55微米,而HBM3目前的凸塊總數(約)為3982個,因此需要大幅增加微型凸塊的總數。

除此之外,業界還將打算在一個模塊中堆疊多達16個內存模塊,即所謂的16-Hi堆疊,這將使得內存供應商能夠顯著提高其HBM堆疊的容量。當然,HBM4將面臨著更大的技術挑戰,晶片的生產難度也將更大。

為此,台積電就曾表示,由於HBM4不是將速度提高了一倍,而是將接口引腳增加了一倍。因此台積電要與所有三家合作夥伴合作,確保三星、美光、海力士等的HBM4(採用台積電的先進封裝方法)符合標準,並確保RDL或interposer或任何介於兩者之間的產品都能支持HBM4的布局和速度。

在HBM的技術發展路線上,SK海力士、三星電子、美光也有著明顯的不同。

海力士正在研究HBM與邏輯處理器直接連接的概念,在混合使用的半導體中將GPU晶片與HBM晶片一起製造。這個想法涉及內存和邏輯製造商共同設計晶片,然後由台積電(TSMC)等晶圓廠運營商製造。

三星正在研究在中間件中使用光子技術,光子通過鏈路的速度比電子編碼的比特更快,而且耗電量更低。除此之外,三星還將HBM堆棧更直接地連接到處理器,這意味著隨著時間的推移,HBM堆棧可以升級,以提供更大的容量,但這需要一個涵蓋該領域的行業標準才有可能實現。

美光目前正在生產HBM3e gen-2內存,採用8層垂直堆疊的24GB晶片。12層垂直堆疊36GB晶片計劃於2024年開始出樣。此外,美光正與半導體代工運營商台積電合作,將其gen-2 HBM3e用於人工智慧和HPC設計應用。

3、HBM市場競爭格局

當前,在HBM市場,只有SK海力士、三星電子和美光三大存儲巨頭能夠量產,因而市場呈現"三分天下"的局面。根據TrendForce,2022年三巨頭分別占據了53%、38%和9%的市場份額。SK海力士由於先發優勢,占據優勢地位,然而隨著三星電子與美光的全力切入,海力士的市場份額將有所下降,預計2024年市場份額分別為SK海力士48%,三星44%,在2025年進一步演變為SK海力士47%,三星45%的市場份額。

在HBM市場份額方面,根據高盛發布研報,受到生成式人工智慧強勁需求的推動,HBM(高帶寬內存)市場規模將從2022年的23億美元增長至2026年的230億美元。高盛認為,HBM市場供不應求的情況未來幾年將持續,SK海力士、三星和美光等主要玩家將持續受益,其中海力士在未來2-3年將保持其50%以上的市場份額。

在更強勁的人工智慧需求推動下,AI伺服器出貨量增加,每個GPU的高帶寬內存(HBM)密度提高,因此我們大幅提高了對HBM市場規模的預期,預計市場規模將增長10倍(4年復合年增長率為77%),從2022年的23億美元增至2026年的230億美元。

儘管供應商計劃大量增加HBM產能以應對強勁的需求增長,但仍存在部分因素(如更低的生產良率)導致行業持續供不應求,預計未來幾年仍將如此。業內的每家HBM供應商都提到,他們2024年的HBM產能已被全部預訂,而2025年的HBM產能也已完成分配,HBM產能分配的增加也推動了傳統DRAM的產業發展。

我們相信,所有主要的DRAM供應商(包括海力士、三星電子和美光)都將受益於HBM市場的強勁增長和市場的供不應求,這將導致持續的HBM溢價,並可能增加每個公司的整體DRAM利潤率。

預計HBM市場將在4年內增長10倍(年均復合增長率為77%),從2022年的23億美元增長到2026年的230億美元,其主要原因在於:

1)更高的晶圓晶片需求和對Nvidia的更高預期;

2)更高的人工智慧訓練伺服器出貨量;

3)更高的行業TSV(矽通孔)容量;

4)每個GPU的HBM質量提升;

5)整個行業向HBM3/HBM3E過渡的速度更快;

6)最新調研顯示HBM需求增強。

因此將2024年HBM市場規模的預期從之前的88億美元上調47%至129億美元,將2025年HBM市場規模的預期上調37%至188億美元,將2026年HBM市場規模的預期上調至230億美元。

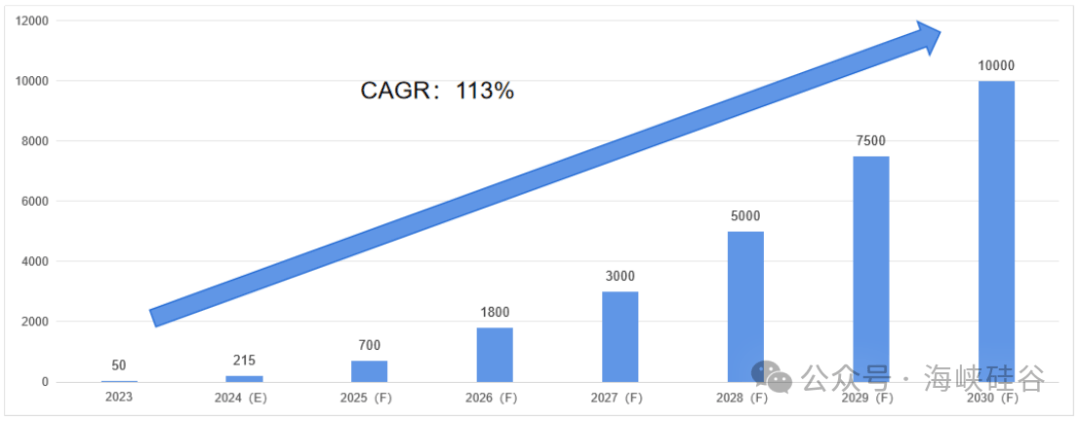

在HBM出貨量方面,2023年11月14日,SK海力士副會長兼聯席CEO朴正浩透露,2023年公司高帶寬內存(HBM)出貨量大幅增加,約為50萬顆,預計到2030年將達到每年1億顆,SK海力士約占全球HBM市場份額約50%。

2023-2030 SK海力士HBM產品出貨量(萬顆)

以一塊GPU配置8塊HBM,每塊HBM採用12層DRAM,進行估算,則至2030年GPU帶動相關產業鏈可形成5000億美元的市場規模。

2030年GPU、HBM、晶圓市場需求預估

(未完待續)