IT之家 10 月 17 日消息,第 70 屆 IEEE 國際電子設備年會(IEDM)將於 2024 年 12 月 7 日至 11 日在舊金山舉行。

屆時,諸如台積電、IMEC、IBM 和三星等各大半導體公司的研究人員將匯聚一堂,分享關於垂直堆疊互補場效應電晶體(CFET)技術的最新研究成果。

儘管 GAA FET(全柵極環繞電晶體)技術還未獲得業界大規模採用,但下一代 CFET 技術已被提上日程,這項技術被視為下一代半導體技術的重要發展方向,有望在未來實現進一步的工藝尺寸微縮。

CFET 的概念最早由 IMEC 研究所於 2018 年提出,即在同一區域內垂直堆疊 n 型和 p 型電晶體。根據 IMEC 的路線圖,CFET 有望在 A5 工藝節點(預計約 2032 年)實現廣泛量產。

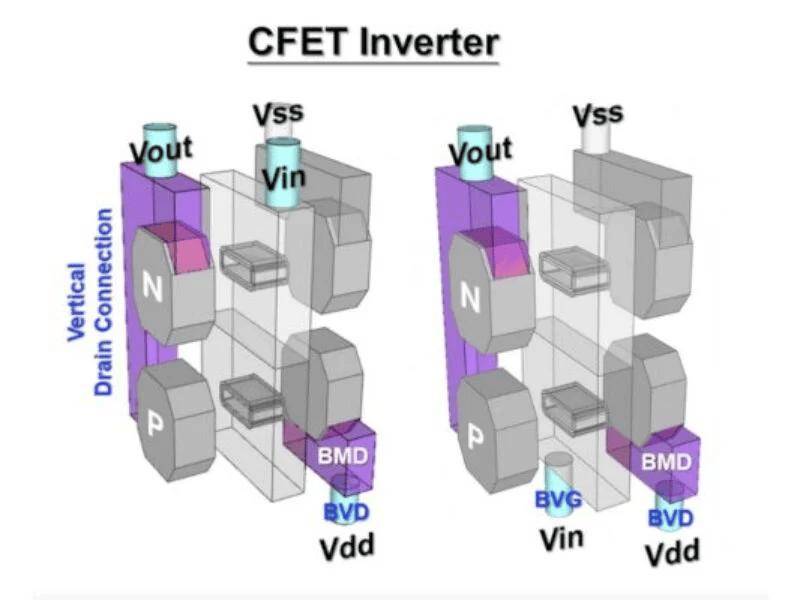

台積電工程師將在會議上發表一篇關於 CFET 的論文,主要是介紹在 48nm 柵距(大致相當於現有 5nm 工藝的標準)上製造的全功能單片 CFET 逆變器的性能。

該逆變器採用堆疊式 n 型和 p 型納米片電晶體,台積電在設計中融入了背面觸點和互連技術,極大地提高了器件的性能與設計靈活性。

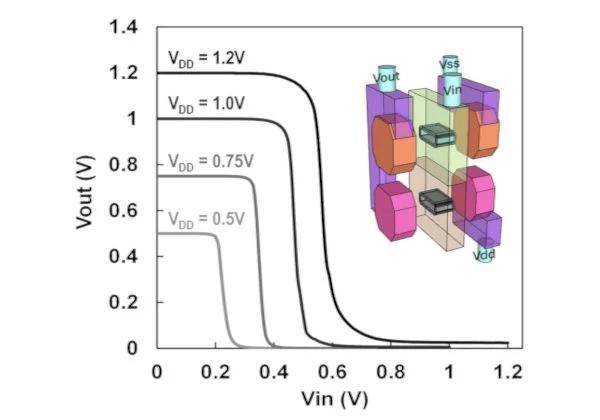

實驗表明,台積電生產的 CFET 器件展現出高達 1.2V 的電壓傳輸特性以及僅 74~76mV / V 的亞閾值斜率,這意味著 CFET 在功耗方面的表現非常出色。

從技術上講,這種架構為未來幾年性能和功耗效率的持續提升以及電晶體密度的增加指明了途徑。雖然這屬於一個重要里程碑,但台積電也承認該技術目前尚未準備好用於商業生產。

IBM 和三星將展示一種「單片堆疊 FET」,這項研究提出了階梯結構的概念,其中底部 FET 通道比上方通道更寬,可降低堆棧高度,並減少高縱橫比工藝帶來的挑戰。

IT之家注意到,IMEC 將展示其在「雙排 CFET」方面的研究成果,旨在進一步在垂直和水平方面擴展 CFET。

IMEC 認為,這種電晶體設計可以在 7A 級工藝節點中變得可行,A7 節點預計將在 1nm(A10)節點後出現,IMEC 路線圖預測 CFET 將於 2032 年左右在 A5 節點進入主流領域。